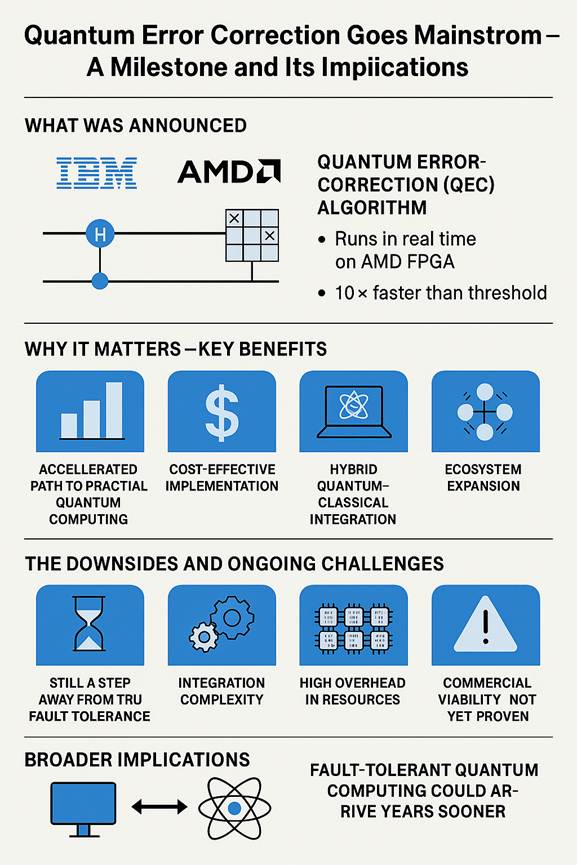

What Was Announced

IBM announced that a key quantum error-correction (QEC) algorithm has been successfully implemented in real-time on a commercially available field-programmable gate array (FPGA) chip manufactured by Advanced Micro Devices (AMD). (Reuters)

Specifically:

- The algorithm is said to run 10 × faster than the threshold required for swapping errors in quantum systems. (Tom’s Hardware)

- It uses off-the-shelf AMD FPGA hardware rather than exclusively bespoke quantum-control electronics. (Reuters)

- The breakthrough comes ahead of schedule for IBM’s roadmap toward a fault-tolerant quantum computer. (IBM Newsroom)

In effect, this development addresses one of the central hurdles in quantum computing: the error correction of fragile quantum bits (qubits) using practical hardware.

Why It Matters (Benefits)

- Scalability of Quantum Systems – By enabling error correction on relatively accessible hardware, the path toward larger, fault-tolerant quantum systems becomes more feasible. Traditional QEC approaches required massive overhead in specialized hardware. The use of FPGA hardware suggests that cost and engineering barriers can be reduced.

- Lower Entry Barrier for Hybrid Quantum-Classical Architectures – The use of commodity or semi-commodity hardware (FPGAs) for QEC means that hybrid architectures (quantum plus classical control) become more plausible. This opens up a broader ecosystem participation, rather than narrowly focused bespoke quantum labs.

- Acceleration of Quantum Deployment Timeline – With QEC hurdles addressed more efficiently, timelines for practical quantum advantage shrink. The “10 × faster than needed” claim signals a performance margin that can provide head-room for system overheads, integration, and real-world deployment.

- Broader Ecosystem & Innovation Potential – Because the hardware is more accessible, more players (academia, industry, cloud providers) may engage in quantum system development, creating a richer ecosystem of tools, algorithms, and hardware convergence.

- Cost-Efficiency Gains – FPGAs are generally more cost-effective and flexible compared to custom ASICs built solely for quantum control. Running QEC on FPGAs suggests a lever for keeping quantum infrastructure costs manageable.

Downsides & Caveats

- Still Not Fully Fault-Tolerant Quantum Computers – While the QEC milestone is significant, this does not yet equate to fully operational, large-scale, fault-tolerant quantum computing. The broader challenges (qubit coherence, connectivity, logical-qubit scaling) remain.

- Engineering & Integration Complexity – Even if the algorithm runs on an FPGA, integrating the error-correction cycle into a full quantum stack (physical qubits → logical qubits → control electronics → application layer) remains highly complex. Practical deployment will demand carefully designed systems and control loops.

- Reliance on FPGAs Brings Its Own Risks – FPGAs, while flexible, bring trade-offs: latency, thermal/performance stability, support infrastructure, and lifecycle issues. Using them for QEC may introduce new failure or reliability modes that need investigation.

- Algorithmic & Hardware Overhead – QEC still imposes resource overhead: many physical qubits per logical qubit, control electronics, feedback loops, etc. The “10× faster” is relative to a threshold—but absolute resource demands may still be high.

- Commercial & Application-Readiness Uncertain – Transitioning from research milestone to commercial infrastructure involves system reliability, operational cost, error rates in real-world settings, and applications that truly benefit from quantum advantage. These factors can delay the realization of business value.

Technology Mechanics – A Closer Look

- Qubits are inherently prone to errors (bit-flip, phase-flip, decoherence) due to physical noise and environmental coupling.

- Quantum error-correction codes (e.g., low-density parity-check codes for quantum, qLDPC) are designed to detect and correct errors across many physical qubits to yield a stable logical qubit. (IBM Newsroom)

- Real-time QEC implies that error detection and correction feedback loops occur within the time window of qubit coherence, so that the system can proceed with computation without excessive downtime or error accumulation.

- The breakthrough: IBM’s algorithm runs on classical FPGA hardware (AMD), meaning that the classical control/decoding portion of QEC can be offloaded to re-programmable logic rather than purpose-built quantum control ASICs. This helps reduce latency and cost. (Reuters)

- The “10× faster than needed” metric suggests that the decoding/control loop latency and throughput exceed the minimum engineering requirement for switching physical errors into corrected logical states.

Implications for Industry & Future Outlook

- Industries anticipating quantum advantage (e.g., materials discovery, logistics/optimization, cryptanalysis) now have a more credible timeline for when quantum systems might become useful, thanks to improved error correction.

- Vendors and hardware providers may pivot more aggressively toward hybrid quantum-classical platforms, leveraging FPGAs or other re-configurable logic as part of the quantum control stack.

- The competitive landscape (including Google, Microsoft, and others) intensifies: breakthroughs like this raise the bar for achieving quantum advantage.

- On the flip side, organizations must temper expectations: quantum advantage is not yet ubiquitous nor guaranteed for all problem domains. Good engineering and application fit remain essential.

- Looking ahead, one should monitor how this QEC capability scales: how many logical qubits can be sustained, how many operations can be executed, what error-rates can be achieved in real-world conditions, and what the cost/power/footprint looks like at scale.

Summary

In summary, IBM’s announcement that a quantum error-correction algorithm runs in real-time on a commercially accessible AMD FPGA chip represents a significant leap forward in making quantum computing more practical. The benefits are clear: improved scalability, lower hardware barriers, and accelerated timelines. The downsides and caveats remain: we are not yet at fully fault-tolerant quantum computers, integration and engineering challenges persist, and commercial readiness is still unfolding.

This development marks a notable inflection point in the quantum computing journey—but as with all major shifts, the devil is in the details of scale-up, system reliability, and application fit.

References

- Reuters. “IBM Says Key Quantum Computing Algorithm Can Run on Conventional AMD Chips.” Reuters Technology News, October 24, 2025. https://www.reuters.com/business/ibm-says-key-quantum-computing-algorithm-can-run-conventional-amd-chips-2025-10-24/

- Tom’s Hardware. “IBM’s Boffins Run a Nifty Quantum Error-Correction Algorithm on Conventional AMD FPGAs.” Tom’s Hardware Tech Industry, October 25, 2025. https://www.tomshardware.com/tech-industry/quantum-computing/ibms-boffins-run-a-nifty-quantum-error-correction-algorithm-on-conventional-amd-fpgas-research-propels-ibms-starling-quantum-computer-project-forward

- IBM Newsroom. “IBM Sets the Course to Build the World’s First Large-Scale, Fault-Tolerant Quantum Computer at Its New Quantum Data Center.” IBM Newsroom, June 10, 2025. https://newsroom.ibm.com/2025-06-10-IBM-Sets-the-Course-to-Build-Worlds-First-Large-Scale%2C-Fault-Tolerant-Quantum-Computer-at-New-IBM-Quantum-Data-Center

- Investopedia. “Why AMD and IBM Shares Just Took Quantum Leaps to Record Highs.” Investopedia Technology & Markets, November 1, 2025. https://www.investopedia.com/amd-ibm-stock-price-record-high-quantum-computing-11836451

Leave a comment